**Philips Semiconductors**

Connectivity

April 2002

# AN10005-01

# ISP1161x Embedded Programming Guide

# **Rev. 1.0**

| Revision History: |      |              |        |  |  |  |  |

|-------------------|------|--------------|--------|--|--|--|--|

| Rev.              | Date | Descriptions | Author |  |  |  |  |

|                   |      |              |        |  |  |  |  |

We welcome your feedback. Send it to <u>wired.support@philips.com</u>

PHILIPS

This is a legal agreement between you (either an individual or an entity) and Philips Semiconductors. By accepting this product, you indicate your agreement to the disclaimer specified as follows:

# DISCLAIMER

PRODUCT IS DEEMED ACCEPTED BY RECIPIENT. THE PRODUCT IS PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, PHILIPS SEMICONDUCTORS FURTHER DISCLAIMS ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANT ABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NONINFRINGEMENT. THE ENTIRE RISK ARISING OUT OF THE USE OR PERFORMANCE OF THE PRODUCT AND DOCUMENTATION REMAINS WITH THE RECIPIENT. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, IN NO EVENT SHALL PHILIPS SEMICONDUCTORS OR ITS SUPPLIERS BE LIABLE FOR ANY CONSEQUENTIAL, INCIDENTAL, DIRECT, INDIRECT, SPECIAL, PUNITIVE, OR OTHER DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF BUSINESS PROFITS, BUSINESS INTERRUPTION, LOSS OF BUSINESS INFORMATION, OR OTHER PECUNIARY LOSS) ARISING OUT OF THIS AGREEMENT OR THE USE OF OR INABILITY TO USE THE PRODUCT, EVEN IF PHILIPS SEMICONDUCTORS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# CONTENTS

| 1. | INTRODUCTION                                                                                                 | 7  |

|----|--------------------------------------------------------------------------------------------------------------|----|

| 2. | ISP1161X SOFTWARE MODELS                                                                                     | 8  |

| 2  | 2.1. Host-Only Mode                                                                                          | 8  |

|    | 2.2. DEVICE-ONLY MODE                                                                                        | 9  |

| 2  | 2.3. SIMULTANEOUS HOST-AND-DEVICE MODE                                                                       | 10 |

| 3. | ISP1161X HARDWARE MODELS                                                                                     | 11 |

| 3  | 8.1 HOST CONTROLLER HARDWARE MODEL                                                                           |    |

| 3  | B.2. DEVICE CONTROLLER HARDWARE MODEL                                                                        | 12 |

| 4. | ISP1161X SOFTWARE ARCHITECTURE                                                                               | 13 |

| 4  | 1.1. USB Host Software Architecture                                                                          |    |

| 4  | I.2. HOST STACK ARCHITECTURE                                                                                 | 14 |

| 4  | I.3. USB DEVICE SOFTWARE ARCHITECTURE                                                                        |    |

| 5. | PROGRAMMING THE HOST CONTROLLER OF ISP1161X                                                                  | 17 |

| 5  | 5.1. SOFTWARE ACCESSIBLE HARDWARE COMPONENTS                                                                 |    |

| 5  | 5.2. HC CONTROL AND STATUS REGISTERS                                                                         |    |

|    | 5.2.1. Writing and Reading of the 16-Bit and 32-Bit Registers                                                |    |

| 5  | 5.3. WRITING AND READING OF THE ATL AND ITL BUFFERS                                                          |    |

| 5  | 5.4. Typical Hardware Initialization Sequence                                                                |    |

|    | 5.4.1. Detecting the Host Controller                                                                         |    |

|    | 5.4.2. Software Resetting the Host Controller                                                                |    |

|    | 5.4.3. Configuring the HcHardwareConfiguration Register                                                      |    |

|    | 5.4.4. Configuring Interrupts                                                                                |    |

|    | 5.4.5. Configuring the HcFmInterval Register                                                                 |    |

|    | 5.4.6. Configuring Root Hub Registers                                                                        |    |

|    | 5.4.7. Setting the ITL and ATL Buffer Lengths                                                                |    |

|    | 5.4.8. Installing INT1 Interrupt Service Routine                                                             |    |

|    | 5.4.9. Setting the Host Controller to the Operational State                                                  |    |

| ٣  | 5.4.10. Setting the Host Controller to Perform USB Enumeration<br>5.5. HOST CONTROLLER DRIVER OPERATION FLOW |    |

| -  |                                                                                                              |    |

| 3  | 5.6. Accessing the ATL Buffer<br>5.6.1. Using SOFITLInt Versus ATLInt                                        |    |

|    | 5.6.2. Starting Scan of the ATL Buffer by Hardware                                                           |    |

| 5  | 5.6.2. Starting Scan of the ATL Buffer by Hardware<br>5.7. ACCESSING THE ITL BUFFER                          |    |

|    | <ul> <li>5.8. FLOWCHART OF THE HOST CONTROLLER IN THE OPERATIONAL MODE</li> </ul>                            |    |

|    | 5.9 SETTING UP PTDs FOR TRANSFERS                                                                            | 42 |

| 0  | 5.9.1. Control Transfer                                                                                      |    |

|    | 5.9.2. Bulk, Interrupt and Isochronous Transfers                                                             |    |

| 5  | 5.10. DATA STRUCTURES FOR LIST PROCESSING                                                                    |    |

| 5  | 5.11. Error Handling                                                                                         |    |

| 6. | PROGRAMMING THE DEVICE CONTROLLER OF ISP1161X                                                                | 49 |

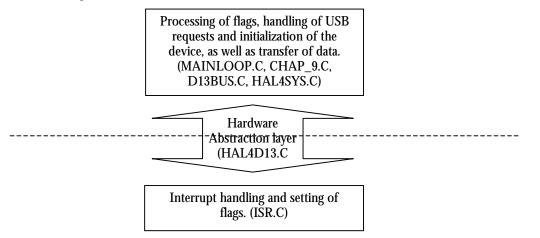

| 6  | 6.1. FIRMWARE STRUCTURE OF THE DEVICE CONTROLLER                                                             |    |

|    | 6.1.1. Hardware Abstraction Layer—HAL4SYS.C                                                                  |    |

|    | 6.1.2. Hardware Abstraction Layer—HAL4D13.C                                                                  |    |

|    | 6.1.3. Interrupt Service Routine—ISR.C                                                                       |    |

|    | 6.1.4. Protocol Layer—CHAP_9.C                                                                               |    |

3

| 6.1.5.         | Protocol Layer—D13BUS.C                                          |    |

|----------------|------------------------------------------------------------------|----|

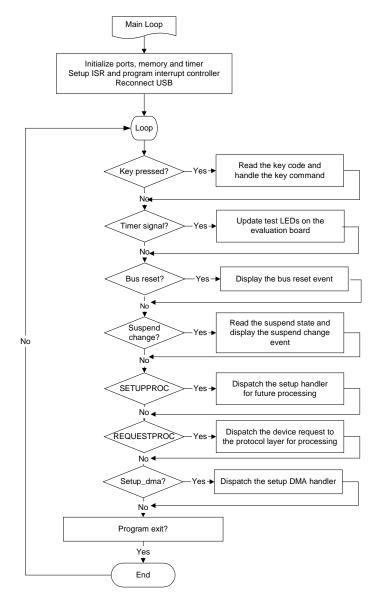

| 6.1.6.         | Main Loop—MAINLOOP.C                                             |    |

| 6.2. Po        | ORTING THE FIRMWARE TO OTHER CPU PLATFORM                        |    |

|                | EVELOPING THE FIRMWARE IN THE POLLING MODE                       |    |

|                | ARDWARE ABSTRACTION LAYER                                        |    |

| 6.4.1.         | Hardware Abstraction Laver for the System                        |    |

| <i>6.4.2.</i>  | Hardware Abstraction Layer for the Device Controller of ISP1161x |    |

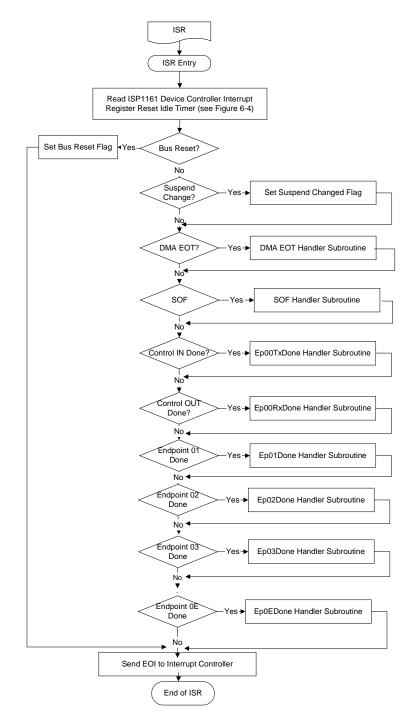

| 6.5. IN        | VTERRUPT SERVICE ROUTINE                                         | 53 |

| 6.5.1.         | Bus Reset                                                        |    |

| 6.5.2.         | Suspend Change                                                   |    |

| <i>6.5.3.</i>  | EÔT Handler                                                      |    |

| 6.5.4          | Control Endpoint Handler                                         |    |

| 6.5.5.         | Control OUT Handler                                              |    |

| 6.5.6          | Control IN Handler                                               | 59 |

| 6.5.7.         | Bulk Endpoint Handler                                            |    |

| <i>6.5.8.</i>  | ISO Endpoint Handler                                             |    |

| 6.6. M         | AIN LOOP                                                         |    |

| 6.7. St        | fandard Device Requests                                          | 70 |

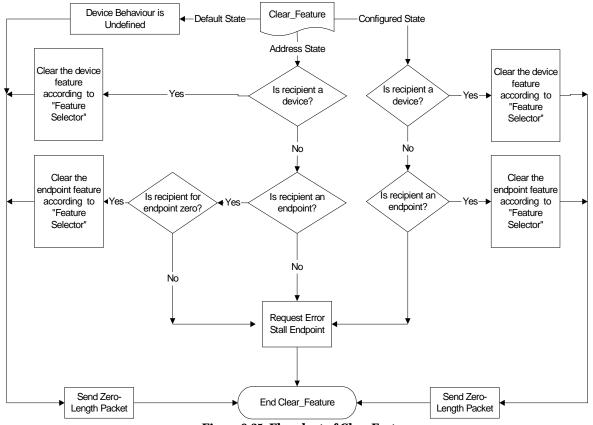

| 6.7.1.         | Clear Feature Request                                            |    |

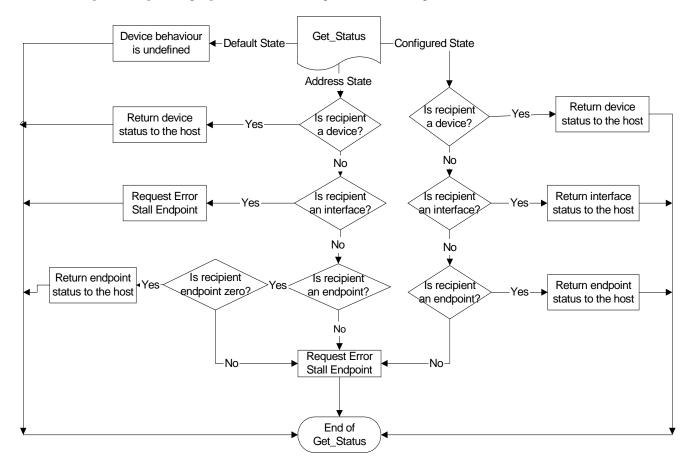

| <i>6.7.2.</i>  | Get Status Request                                               |    |

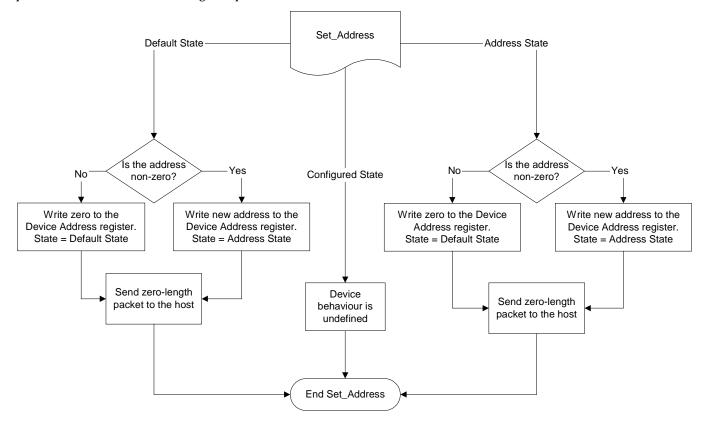

| <i>6.7.3.</i>  | Set Address Request                                              | 73 |

| 6.7.4          | Get Configuration Request                                        |    |

| 6.7.5.         | Get Descriptor Request                                           | 75 |

| <i>6.7.6.</i>  | Set Configuration Request                                        |    |

| 6.7.7.         | Get and Set Interface Requests                                   |    |

| <i>6.7.8</i> . | Set Feature Request                                              |    |

| <i>6.7.9.</i>  | Class Request                                                    |    |

| 6.8. V         | ENDOR REQUEST                                                    |    |

| <i>6.8.1.</i>  | Vendor Request for the Bulk Transfer                             |    |

| 6.8.2          | CATC Capture of a PIO OUT Transfer                               |    |

| <i>6.8.3.</i>  | CATC Capture of a PIO IN Transfer                                |    |

| <i>6.8.4.</i>  | Vendor Request for the ISO Transfer                              | 81 |

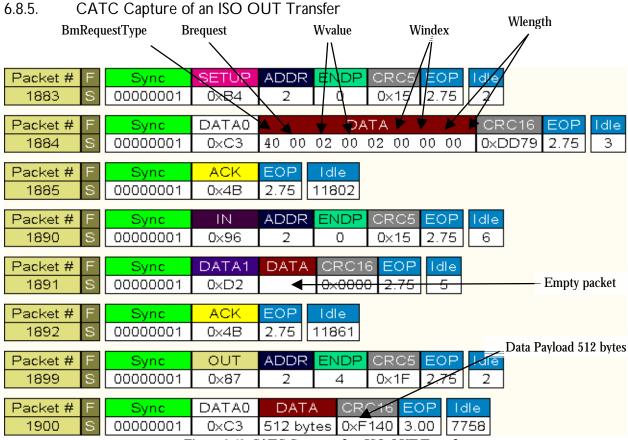

| 6.8.5          | CATC Capture of an ISO OUT Transfer                              |    |

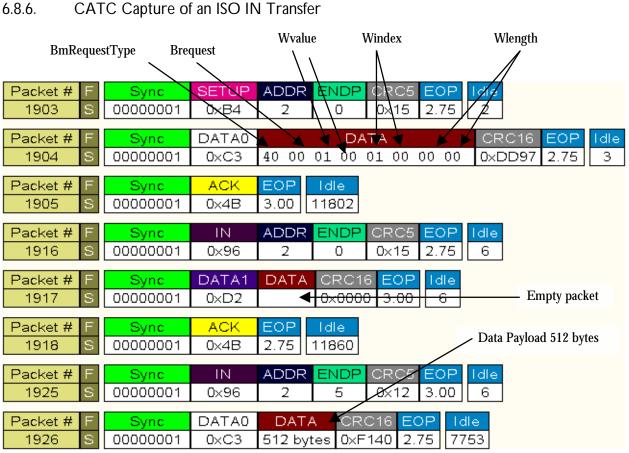

| <i>6.8.6.</i>  | CATC Capture of an ISO IN Transfer                               | 82 |

| 7. REFE        | RENCES                                                           |    |

# **TABLES**

| Table 5-1: HC Control and Status Register Summary                                                            | 18 |

|--------------------------------------------------------------------------------------------------------------|----|

| Table 5-1: HC Control and Status Register Summary         Table 5-2: HcScratch Register: Bit Allocation      | 23 |

| Table 5-3: HcCommandStatus Register: Bit Allocation         Table 5-4: HcControl Register: Bit Allocation    | 24 |

| Table 5-4: HcControl Register: Bit Allocation                                                                | 24 |

| Table 5-5: HcHardwareConfiguration Register: Bit Allocation                                                  | 26 |

| Table 5-6: HcHardwareConfiguration Register: Bit Description                                                 | 26 |

| Table 5-7: HcInterruptEnable Register: Bit Allocation                                                        | 27 |

| Table 5-8: HcµPInterruptEnable Register: Bit Allocation                                                      | 28 |

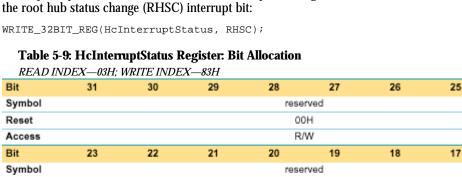

| Table 5-9: HcInterruptStatus Register: Bit Allocation                                                        | 29 |

| Table 5-10: HcµPInterrupt Register: Bit Allocation                                                           | 29 |

| Table 5-11 HcFmInterval Register: Bit Allocation                                                             | 30 |

| Table 5-12: HcRhDescriptorA Register: Bit Allocation         Table 5-13: HcRhStatus Register: Bit Allocation | 31 |

| Table 5-13: HcRhStatus Register: Bit Allocation                                                              | 32 |

| Table 5-14: HcRhDescriptorB Register: Bit Allocation                                                         | 32 |

| Table 5-15: USB Transaction Error Codes                                                                      | 48 |

| Table 6-1: Building Blocks Modifications                                                                     | 50 |

|                                                                                                              |    |

| Table 6-2: Interrupt Register: Bit Allocation                                                             | 54 |

|-----------------------------------------------------------------------------------------------------------|----|

| Table 6-2: Interrupt Register: Bit Allocation         Table 6-3: Endpoint Status Register: Bit Allocation | 58 |

| Table 6-4: Endpoint Status Register: Bit Description                                                      | 59 |

| Table 6-5: Recommended Endpoint Configuration Register Programming for a Bulk Endpoint                    | 61 |

| Table 6-6: Endpoint Configuration Register: Bit Allocation                                                | 61 |

| Table 6-7: Endpoint Configuration Register: Bit Description                                               |    |

| Table 6-8: Recommended Endpoint Configuration Register Programming for an ISO Endpoint                    |    |

| Table 6-9: Mode Register: Bit Allocation                                                                  | 69 |

| Table 6-10: Mode Register: Bit Description                                                                | 69 |

| Table 6-11: Device Address Register: Bit Allocation                                                       |    |

| Table 6-12: Device Address Register: Bit Description                                                      | 74 |

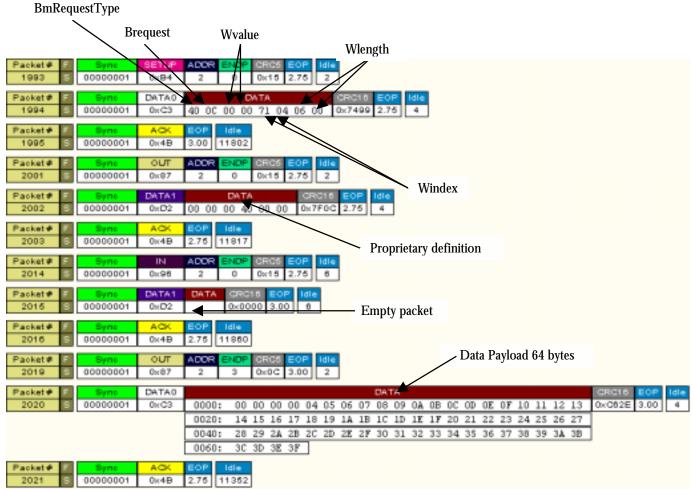

| Table 6-13: Device Request                                                                                | 78 |

| Table 6-14: Proprietary Definition of the Sample Firmware and Applet                                      | 79 |

| Table 6-15: Device Request                                                                                | 81 |

| •                                                                                                         |    |

# **FIGURES**

| Figure 2-1: ISP1161x Host-Only Mode Software Model                                 | 8  |

|------------------------------------------------------------------------------------|----|

| Figure 2-2: ISP1161x Device-Only Mode Software Model                               | 9  |

| Figure 2-3: ISP1161x Simultaneous Host-and-Device Mode Software Model              | 10 |

| Figure 3-1: ISP1161x Host Controller Hardware Model                                | 11 |

| Figure 3-2: ISP1161x Device Controller Hardware Model                              | 12 |

| Figure 4-1: USB Host Software Architecture                                         | 13 |

| Figure 4-2: Host Stack Architecture                                                |    |

| Figure 4-3: Host Stack Calling Sequence Example                                    |    |

| Figure 4-4: USB Device Software Architecture                                       | 16 |

| Figure 5-1: 16-Bit Register Access Cycle                                           | 19 |

| Figure 5-2: 32-Bit Register Access Cycle                                           | 19 |

| Figure 5-3: Code Example for 32-Bit Register Write                                 | 20 |

| Figure 5-4: Code Example for 32-Bit Register Read                                  |    |

| Figure 5-5: Code Example for 16-Bit Register Read                                  |    |

| Figure 5-6: Code Example for 16-Bit Register Write                                 |    |

| Figure 5-7: Code Example for Writing to the ATL Buffer                             |    |

| Figure 5-8: Code Example for Detecting the Host Controller                         |    |

| Figure 5-9: Code Example for Resetting the Host Controller                         |    |

| Figure 5-10: Code Example for Setting the Host Controller to the RESET State       |    |

| Figure 5-11: Code Example for Initializing the HcHardwareConfiguration Register    | 27 |

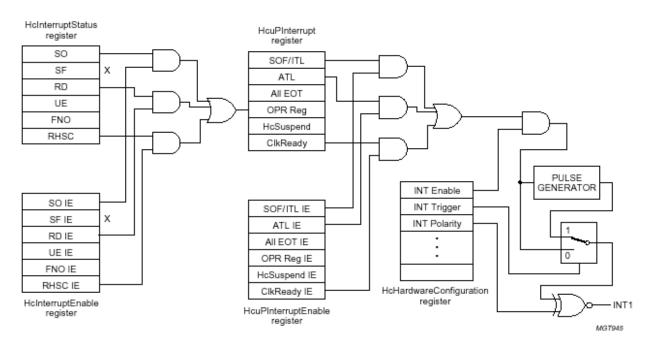

| Figure 5-12: ISP1161x Host Controller Interrupt Logic                              | 28 |

| Figure 5-13: Code Example for Initializing the Host Controller Interrupt           | 29 |

| Figure 5-14: Code Example for Initializing the HcDescriptorA Register              |    |

| Figure 5-15: Code Example for Initializing the HcRhStatus Register                 | 31 |

| Figure 5-16: Code Example for Setting the ATL and ITL Buffer Lengths               | 33 |

| Figure 5-17: Code Example for Setting the Host Controller to the Operational State |    |

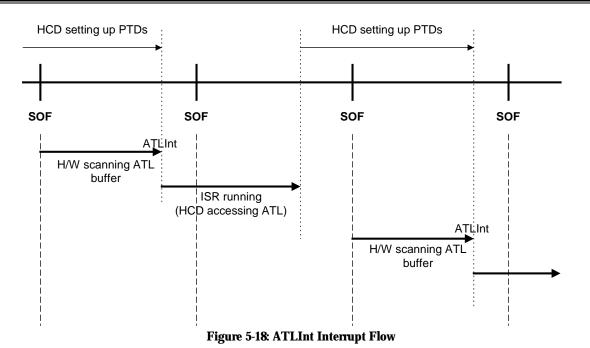

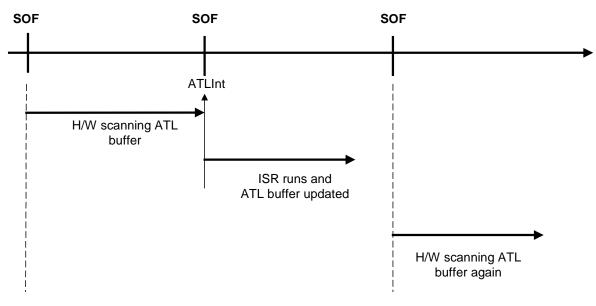

| Figure 5-18: ATLInt Interrupt Flow                                                 | 37 |

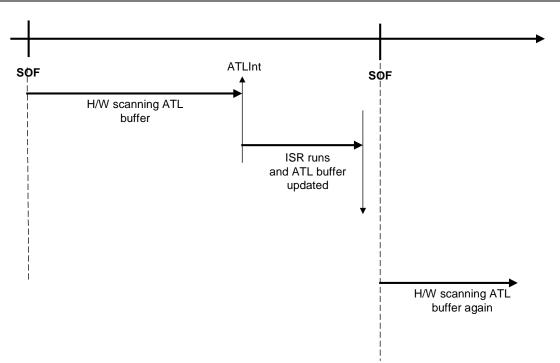

| Figure 5-19: Running the Host Controller with the ATLInt Interrupt                 | 38 |

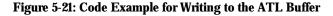

| Figure 5-20: Running the Host Controller with the SOFITLInt Interrupt              | 38 |

| Figure 5-21: Code Example for Writing to the ATL Buffer                            | 39 |

| Figure 5-22: Code Example for Reading from the ATL Buffer                          | 40 |

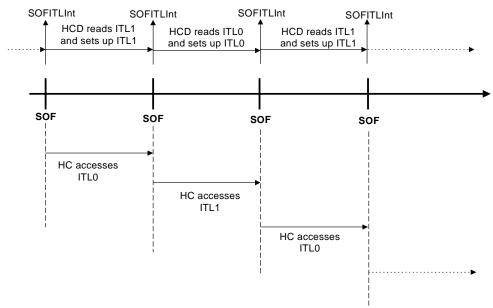

| Figure 5-23: ITL Buffer Access Flow                                                | 40 |

| Figure 5-24: Code Example for Writing to the ITL Buffer                            | 41 |

| Figure 5-25: Code Example for Reading from the ITL Buffer                          | 41 |

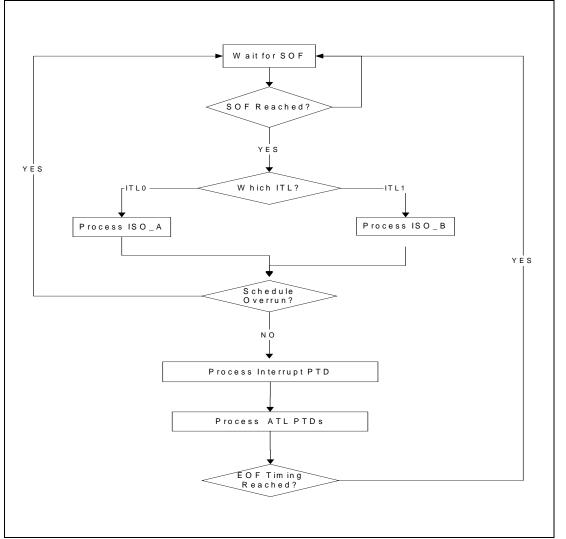

| Figure 5-26: Host Controller in the Operational State Flow Chart                   | 42 |

| Figure 5-27: PTD Header Fields                                                     |    |

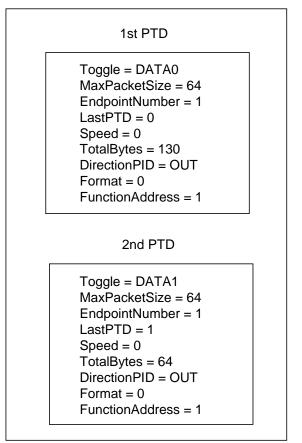

| Figure 5-28: PTD Flow for the Control Transfer                                     | 45 |

| Figure 5-29: Data Toggle Bit Setting Example Across Multiple PTDs                                                                                    | 46       |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 5-30: Data Toggle Bit Setting in Multiple PTD Data Packets                                                                                    |          |

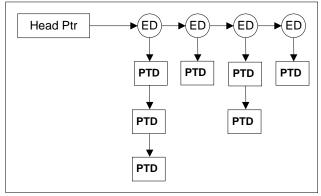

| Figure 5-31: Typical List Structure                                                                                                                  | 47       |

| Figure 5-32: List Processing Data Structure                                                                                                          | 48       |

| Figure 6-1: Firmware Structure of the ISP1161x Device Controller                                                                                     | 49       |

| Figure 6-2: Flowchart of ISR                                                                                                                         | 53       |

| Figure 6-3: Code Example of a Typical ISR                                                                                                            | 54       |

| Figure 6-4: Code Example to Read the Interrupt Register                                                                                              | 55       |

|                                                                                                                                                      |          |

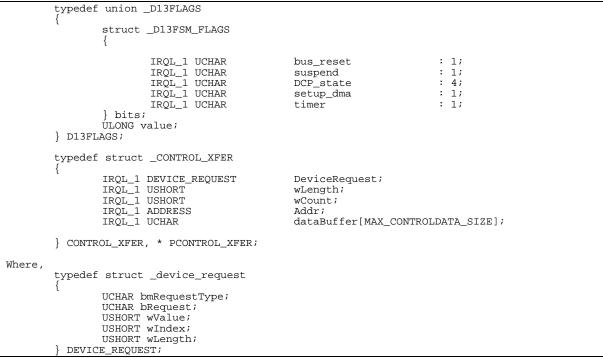

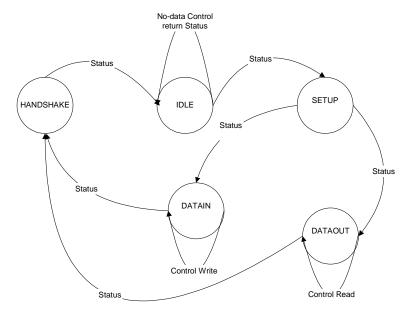

| Figure 6-5: Control Flags<br>Figure 6-6: State Machine of the Control Transfer                                                                       | 56       |

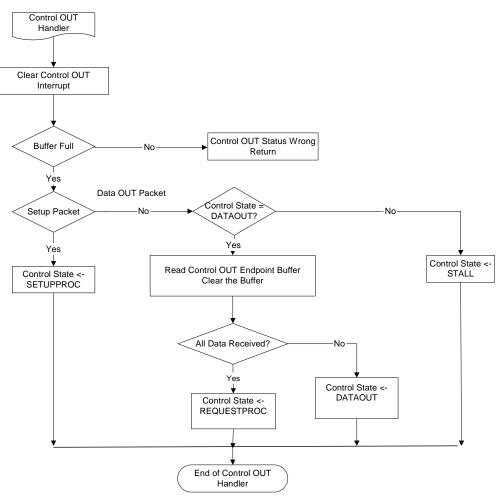

| Figure 6-7: Flowchart of the Control OUT Handler                                                                                                     | 57       |

| Figure 6-8: Code Example to Check Status of the OUT Endpoint                                                                                         |          |

| Figure 6-9: Code Example for Reading the Endpoint Status Register                                                                                    |          |

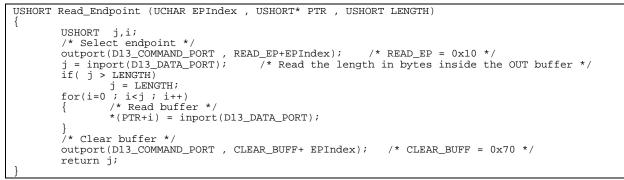

| Figure 6-10: Code Example for Reading the Contents of an OUT Buffer                                                                                  |          |

| Figure 6-11: Code Example for Reading the Endpoint Status Register                                                                                   |          |

| Figure 6-12: Code Example to Check the Status of the IN Endpoint.                                                                                    |          |

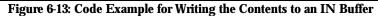

| Figure 6-13: Code Example for Writing the Contents to an IN Buffer                                                                                   |          |

| Figure 6-14: Flowchart of the Control IN Handler                                                                                                     | 60       |

| Figure 6-15: Code Example for Configuring a Bulk OUT or Bulk IN Endpoint                                                                             | 62       |

| Figure 6-16: Function Definition of void SetEndpointConfig(UCHAR bEPConfig, UCHAR bEPIndex)                                                          | 62       |

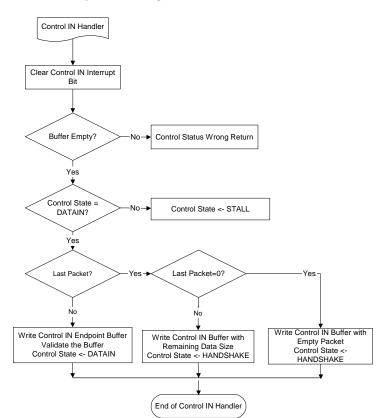

| Figure 6-17: Flowchart of the Bulk OUT Handler                                                                                                       | 62       |

| Figure 6-18: Code Example for Reading the Endpoint Status Register                                                                                   |          |

| Figure 6-19: Code Example to Check the Status of the Bulk OUT Endpoint.                                                                              | 63       |

| Figure 6-20: Code Example for Reading the Contents of a Bulk OUT Buffer                                                                              | 63       |

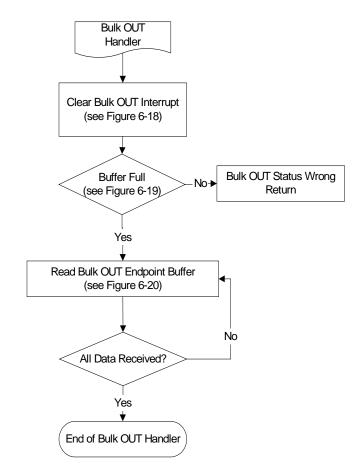

| Figure 6-21: Flowchart of the Bulk IN Handler                                                                                                        | 61       |

| Figure 6-22: Code Example for Reading the Endpoint Status Register                                                                                   |          |

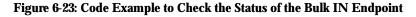

| Figure 6-23: Code Example to Check the Status of the Bulk IN Endpoint                                                                                | 61       |

| Figure 6-24: Code Example to Check the Status of the Burk IN Endpoint                                                                                | 65       |

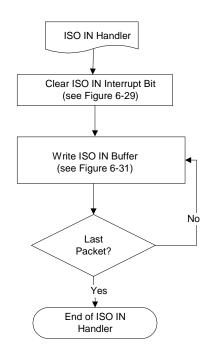

| Figure 6-25: Code Example for Writing the Contents into a bluk Ity Burlet<br>Figure 6-25: Code Example for Configuring an ISO OUT or ISO IN Endpoint |          |

| Figure 6-26: Function Definition of void SetEndpointConfig(UCHAR bEPConfig, UCHAR bEPIndex)                                                          | 0J<br>65 |

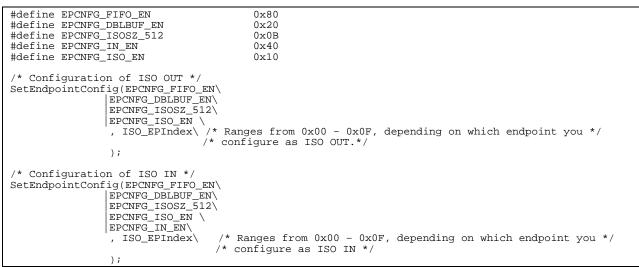

| Figure 6-27: Flowchart of the ISO OUT Handler                                                                                                        | 66       |

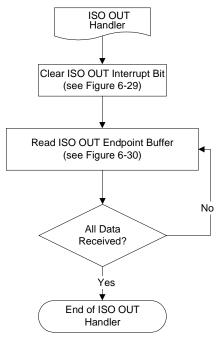

| Figure 6-28: Flowchart of the ISO IN Handler                                                                                                         | 00       |

| Figure 6-29: Code Example for Reading the Endpoint Status Register                                                                                   | 00       |

| Figure 6-23. Coue Example for Reading from an ISO Endpoint Puffer                                                                                    | 07       |

| Figure 6-30: Code Example for Reading from an ISO Endpoint Buffer                                                                                    | 07       |

| Figure 6-31: Code Example for Writing to an ISO Endpoint Buffer<br>Figure 6-32: Flowchart of the Main Loop                                           | 07<br>60 |

| Figure 6-32. Flowchart of the Main Loop                                                                                                              | 00       |

| Figure 6-33: Code Example for Writing to the Mode Register                                                                                           | 09       |

| Figure 6-34: Code Example on Setting SoftConnect<br>Figure 6-35: Flowchart of Clear Feature                                                          | 09       |

|                                                                                                                                                      |          |

| Figure 6-36: Code Example to Send Zero-Length Packet                                                                                                 | /1       |

| Figure 6-37: Code Example to Stall or Unstall an Endpoint                                                                                            |          |

| Figure 6-38: Flowchart of Get Status                                                                                                                 |          |

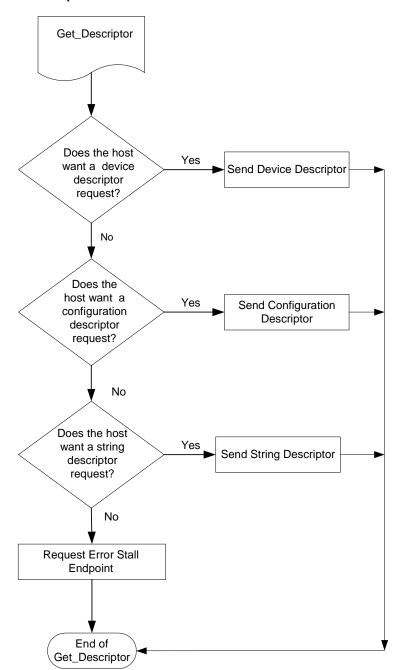

| Figure 6-39: Flowchart of Set Address                                                                                                                |          |

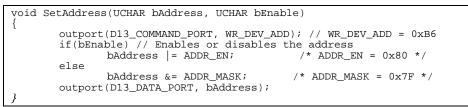

| Figure 6-40: Code Example of the Set Address Routine                                                                                                 |          |

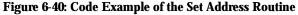

| Figure 6-41: Flowchart of Get Configuration                                                                                                          |          |

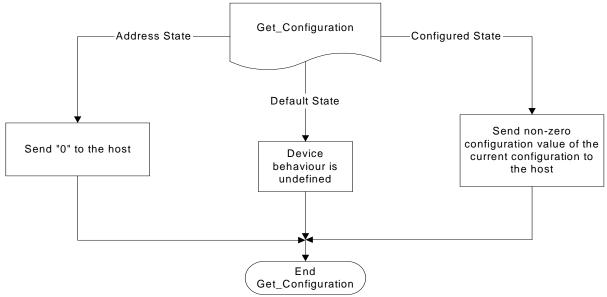

| Figure 6-42: Flowchart of Get Descriptor                                                                                                             |          |

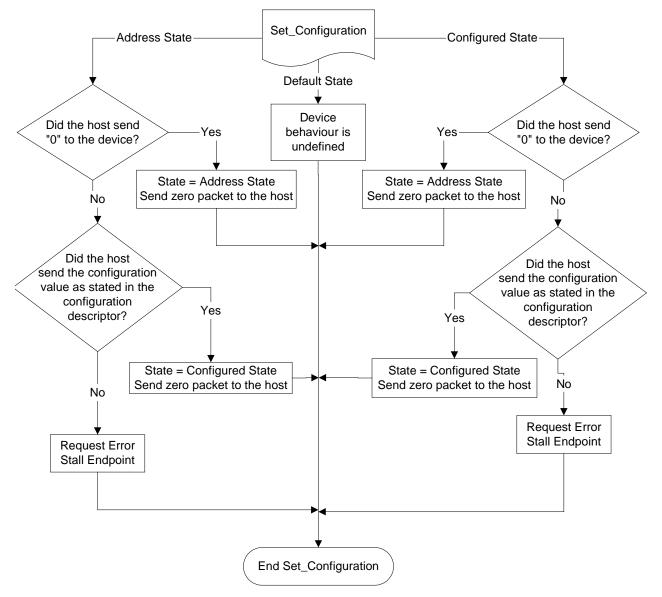

| Figure 6-43: Flowchart of Set Configuration                                                                                                          |          |

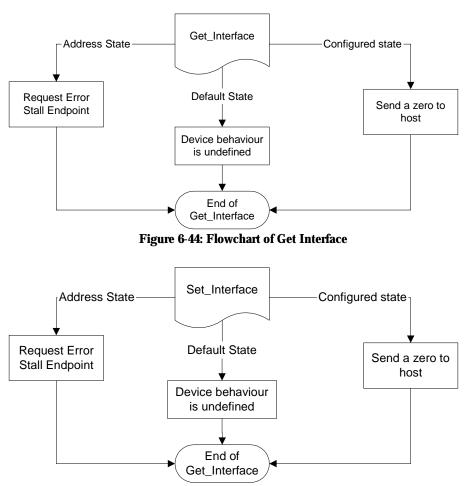

| Figure 6-44: Flowchart of Get Interface                                                                                                              |          |

| Figure 6-45: Flowchart of Set Interface                                                                                                              |          |

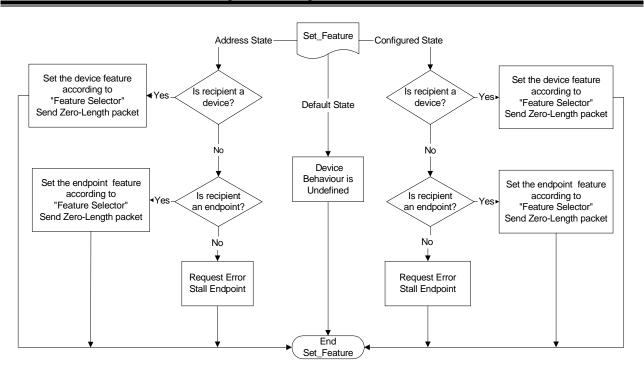

| Figure 6-46: Flowchart of Set Feature                                                                                                                |          |

| Figure 6-47: CATC Capture of a PIO OUT Transfer                                                                                                      |          |

| Figure 6-48: CATC Capture of a PIO IN Transfer                                                                                                       |          |

| Figure 6-49: CATC Capture of an ISO OUT Transfer                                                                                                     |          |

| Figure 6-50: CATC Capture of an ISO IN Transfer                                                                                                      | 82       |

6

# 1. Introduction

ISP1161x (denotes ISP1161 and ISP1161A) is a single-chip Universal Serial Bus (USB) Host Controller (HC) and Device Controller (DC) that complies with *Universal Serial Bus Specification Rev. 2.0 (Full Speed)*. These two USB controllers—the Host Controller and the Device Controller—share the same microprocessor bus interface. These controllers have the same data bus, but different I/O locations. They also have separate interrupt request output pins, separate direct memory access (DMA) channels that include separate DMA request output pins (DREQ) and DMA acknowledge input pins (DACK). This makes it possible for a microprocessor to control both the USB Host Controller and the USB Device Controller at the same time.

ISP1161x provides two downstream ports for the USB Host Controller and one upstream port for the USB Device Controller. Each downstream port has its own overcurrent (OC) detection input pin and power supply switching control output pin. The upstream port has its own  $V_{BUS}$  detection input pin. ISP1161x also provides separate wake-up input pins and suspended status output pins for the USB Host Controller and the USB Device Controller, respectively. This makes power management flexible. The downstream ports for the Host Controller can be connected to any USB compliant USB devices and USB hubs that have USB upstream ports. The upstream port for the Device Controller can be connected to any USB compliant USB host and USB hubs that have USB downstream ports.

The Host Controller is adapted from *Open Host Controller Interface Specification for USB, Release: 1.0a* referred to as OHCI in the rest of this document.

The Device Controller is compliant with most device class specifications, such as Imaging Class, Mass Storage Devices, Communication Devices, Printing Devices and Human Interface Devices. ISP1161x is well suited for embedded systems and portable devices that require a USB host only, a USB device only, or a combined and configurable USB host and USB device capabilities. ISP1161x provides high flexibility to the systems that have it built-in. For example, a system that has ISP1161x built-in allows it not only to be connected to a PC or USB hub that has a USB downstream port, but also to be connected to a device that has a USB upstream port, such as USB printer, USB camera, USB keyboard and USB mouse, among others. ISP1161x enables point-to-point connectivity between embedded systems. An interesting application example is to connect a ISP1161x Host Controller with a ISP1161x Device Controller.

# 2. ISP1161x Software Models

As ISP1161x can function in one of the three modes—host-only mode, device-only mode and simultaneous host-and-device mode—each mode of operation adopts a different software model.

### 2.1. Host-Only Mode

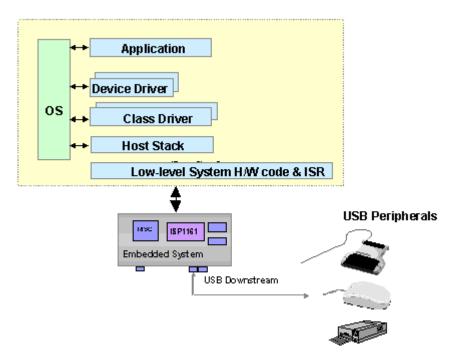

The host-only mode software model consists of the host stack, one or more class drivers, zero or more device drivers, and the application. Figure 2-1 shows the data flow and the call hierarchy of the software components in this software model.

Figure 2-1: ISP1161x Host-Only Mode Software Model

Since a single USB Host Controller can have multiple USB slave devices connected to it, the host-only mode software model can contain multiple class drivers, in which each class driver services each type of USB slave device. Usually, the application accesses class drivers directly to perform USB operations. However, in some cases, it makes sense to have one more layer, dubbed Device Driver, between the class driver and the application. For example, you can have device drivers for different types of printers in which these device drivers access one common USB printer class driver to perform operations on printers.

### 2.2. Device-Only Mode

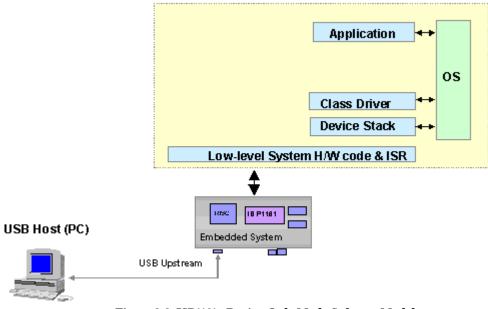

The software model for the device-only mode consists of the device stack, a class driver and the application. The data flow and the call hierarchy of the software components in this software model are given in Figure 2-2.

Figure 2-2: ISP1161x Device-Only Mode Software Model

Since a USB slave device performs a single class of functions, there must only be one class driver for a USB slave device. The application accesses the class driver when performing USB operations.

### 2.3. Simultaneous Host-and-Device Mode

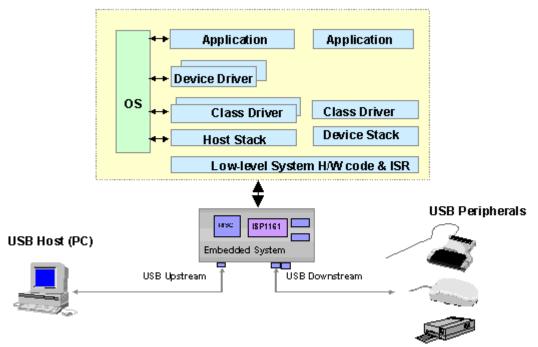

The most versatile mode of ISP1161x is the simultaneous host-and-device mode. The software model for this mode is realized by combining the host-only mode and device-only mode software models into a single model. The resulting software model is depicted in Figure 2-3.

Figure 2-3: ISP1161x Simultaneous Host-and-Device Mode Software Model

In this mode, ISP1161x functions as if there are separate USB Host and Device Controllers. The software model for this mode requires no interdependencies between the host-side portion and the device-side portion of the software. In other words, the device-side software runs totally independent of the host-side software.

# 3. ISP1161x Hardware Models

### 3.1. Host Controller Hardware Model

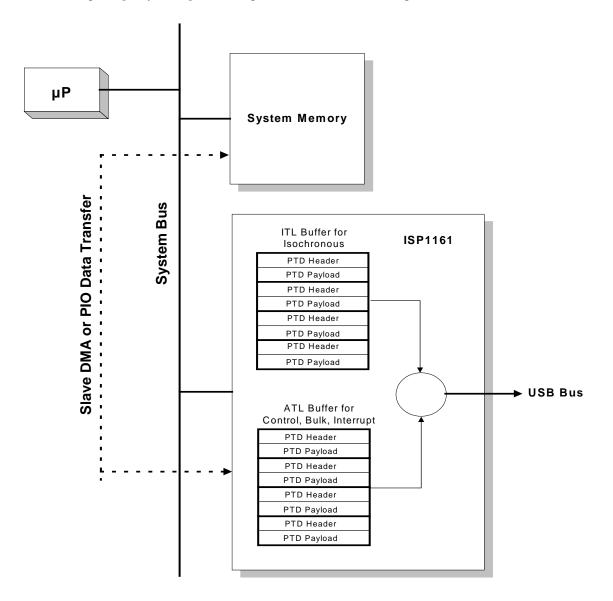

The major difference between the OHCI Host Controller and ISP1161x is that the OHCI Host Controller is a busmaster device whereas ISP1161x is not. In the OHCI Host Controller, the USB data packet is sent from and received in the system memory by the bus master DMA present in the OHCI Host Controller. However, in ISP1161x, the microprocessor is responsible for moving the USB data packet between the system memory, and the ITL and ATL buffers inside ISP1161x. An I/O bus interface and the bus master DMA are eliminated from ISP1161x, and therefore, the term "slave Host Controller". This is because ISP1161x is intended to be used for embedded applications in which cost and design simplicity are important design considerations for choosing a Host Controller IC.

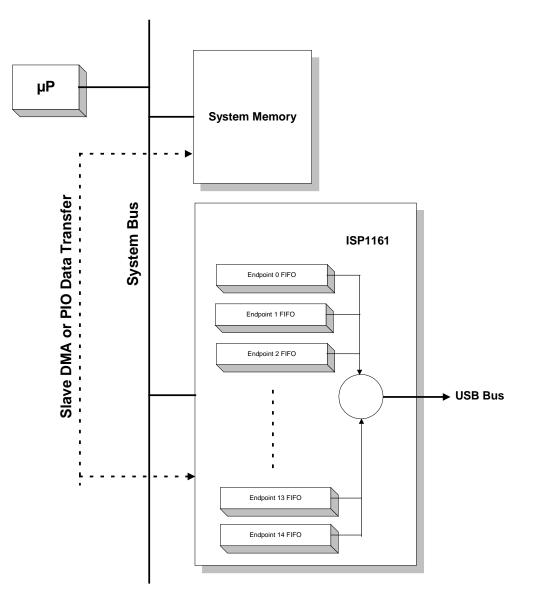

### 3.2. Device Controller Hardware Model

When the Device Controller part of ISP1161x is in operation, the microprocessor moves the USB packet data between the system memory and endpoint FIFOs via Programmed I/O (PIO) or slave DMA built into ISP1161x. USB packets are sent from and received in endpoint FIFOs.

# 4. ISP1161x Software Architecture

### 4.1. USB Host Software Architecture

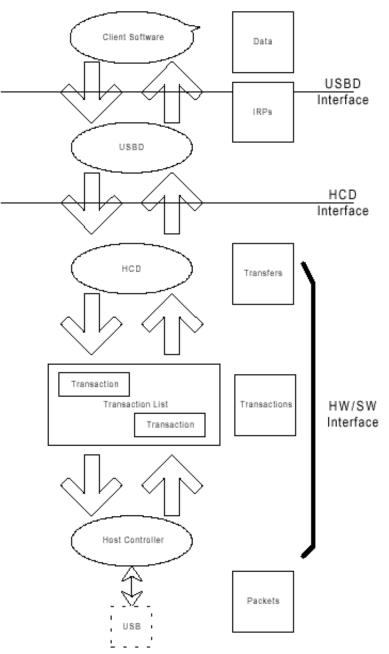

Figure 4-1: USB Host Software Architecture

As can be seen in Figure 4-1, the USB host software architecture includes the Universal Serial Bus Driver (USBD), the Host Controller Driver (HCD) and the client software. The client software can be the application code or USB class drivers. The USBD and the HCD are collectively referred to as the USB host stack. In the USB host stack, the USBD deals with hardware-independent protocol related aspects of USB whereas the HCD deals with hardware-dependent

protocol related aspects of USB. Therefore, it is the HCD that accesses the USB Host Controller hardware. In other words, the HCD drives the Host Controller by manipulating programmable hardware registers inside the Host Controller. This document explains how to program the Host Controller hardware of ISP1161x to enable it to perform HCD functions when it runs as a USB Host Controller.

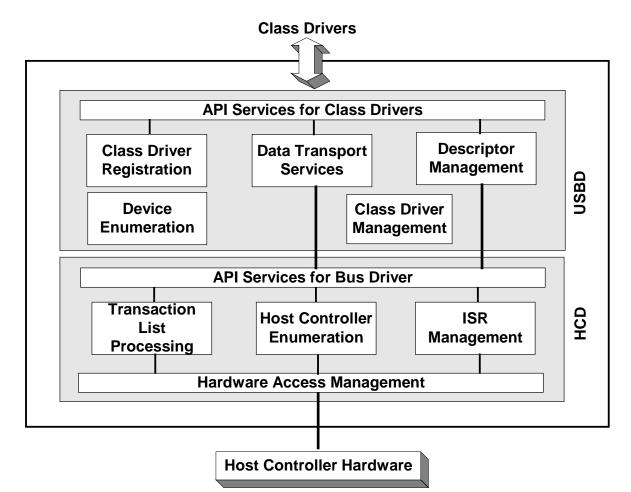

### 4.2. Host Stack Architecture

Figure 4-2 shows the major functions built in a USB host stack.

#### Figure 4-2: Host Stack Architecture

The typical sequence of calls that occurs when performing a USB transfer is as follows:

- 1. The application initiates a write or read over the USB bus.

- 2. The class driver calls USBD APIs for the write or read initiated by the application.

- 3. USBD APIs call HCD APIs on behalf of the calling class driver.

- 4. HCD APIs cause USB transactions to occur.

- 5. The class driver is notified that the transfer is complete.

- 6. The application is notified of the transfer completion.

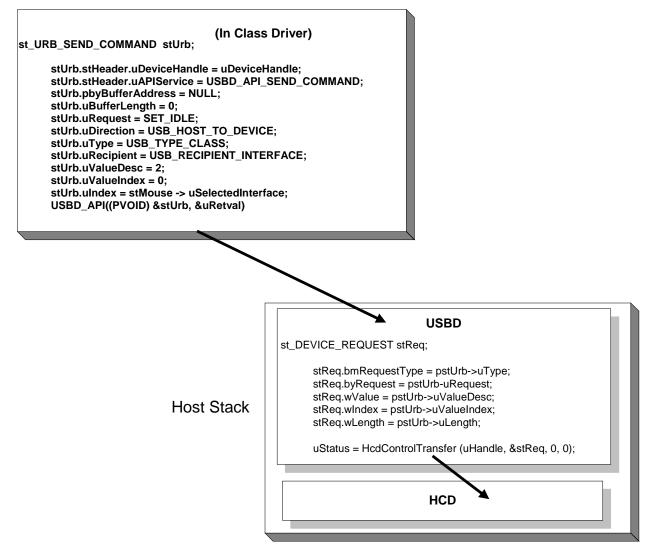

The following example shows the call sequence from the class driver to the USBD and the HCD in a host stack implementation.

Figure 4-3: Host Stack Calling Sequence Example

In this example, the *USBD\_API()* call (in the class driver box) is the calling mechanism for calling USBD APIs. The *HcdControlTransfer()* function is one of the available HCD APIs and it does a control transfer.

### 4.3. USB Device Software Architecture

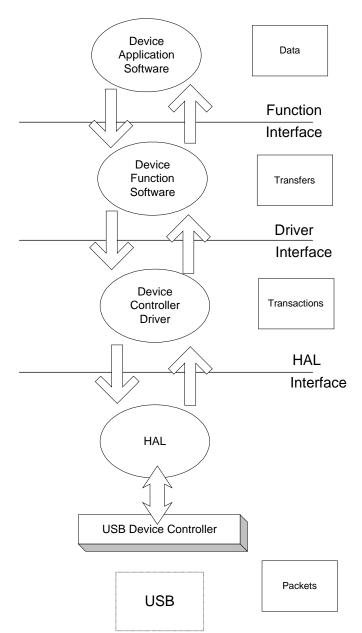

Figure 4-4: USB Device Software Architecture

A USB device is a slave device, and its job is to respond to requests sent by the host. The Device Controller Driver responds to requests on its own, if these requests are standard requests, that is, USB standard requests. If these requests are function specific, that is, class requests, the Device Controller Driver passes them to the device function software. The device function software in conjunction with the device application software handle these requests and send responses to the host. Logically, the Device Controller Driver interacts with the USBD on the host side and the device function software interacts with the host class driver.

16

# **5.** Programming the Host Controller of ISP1161x

### 5.1. Software Accessible Hardware Components

The major hardware components of the Host Controller in ISP1161x that are accessible by software are:

- HC control and status registers

- ATL buffer

- ITL buffer.

### 5.2. HC Control and Status Registers

The HC control and status registers in ISP1161x include a set of operational OHCI compliant registers (32-bit wide) and a set of ISP1161x specific registers (16-bit wide). Each read/write register has a set of two offset indices: one for the read access and the other for the write access. Read-only or write-only registers have only one offset index. For convenience, the command-write operation, can be ORed with 0x80, so that only one value is required to be defined for each register. The offset indices for the HC control and status registers are given in Table 5-1.

| Table 5-1 | 1: HC Control | and Status Register Summary |       |                                 |

|-----------|---------------|-----------------------------|-------|---------------------------------|

| Comm      | and (Hex)     | Register                    | Width | Functionality                   |

| Read      | Write         |                             |       |                                 |

| 00        | N/A           | HcRevision                  | 32    | HC Control and Status Registers |

| 01        | 81            | HcControl                   | 32    |                                 |

| 02        | 82            | HcCommandStatus             | 32    | -                               |

| 03        | 83            | HcInterruptStatus           | 32    | -                               |

| 04        | 84            | HcInterruptEnable           | 32    |                                 |

| 05        | 85            | HcInterruptDisable          | 32    | -                               |

| 0D        | 8D            | HcFmInterval                | 32    | HC Frame Counter Registers      |

| 0E        | N/A           | HcFmRemaining               | 32    |                                 |

| 0F        | N/A           | HcFmNumber                  | 32    | -                               |

| 11        | 91            | HcLSThreshold               | 32    | -                               |

| 12        | 92            | HcRhDescriptorA             | 32    | HC Root Hub Registers           |

| 13        | 93            | HcRhDescriptorB             | 32    | -                               |

| 14        | 94            | HcRhStatus                  | 32    |                                 |

| 15        | 95            | HcRhPortStatus[1]           | 32    | -                               |

| 16        | 96            | HcRhPortStatus[2]           | 32    | -                               |

| 20        | A0            | HcHardwareConfiguration     | 16    | HC DMA and Interrupt Control    |

| 21        | A1            | HcDMAConfiguration          | 16    | Registers                       |

| 22        | A2            | HcTransferCounter           | 16    | -                               |

| 24        | A4            | HcµPInterrupt               | 16    |                                 |

| 25        | A5            | HcµPInterruptEnable         | 16    | -                               |

| 27        | N/A           | HcChipID                    | 16    | HC Miscellaneous Registers      |

| 28        | A8            | HcScratch                   | 16    |                                 |

| N/A       | A9            | HcSoftwareReset             | 16    | _                               |

| 2A        | AA            | HcITLBufferLength           | 16    | HC Buffer RAM Control Registers |

| 2B        | AB            | HcATLBufferLength           | 16    | _                               |

| 2C        | N/A           | HcBufferStatus              | 16    |                                 |

| 2D        | N/A           | HcReadBackITL0Length        | 16    |                                 |

| 2E        | N/A           | HcReadBackITL1Length        | 16    | _                               |

| 40        | C0            | HcITLBufferPort             | 16    | _                               |

| 41        | C1            | HcATLBufferPort             | 16    |                                 |

|           |               |                             |       |                                 |

#### Table 5-1: HC Control and Status Register Summary

Rev. 1.0

5.2.1. Writing and Reading of the 16-Bit and 32-Bit Registers

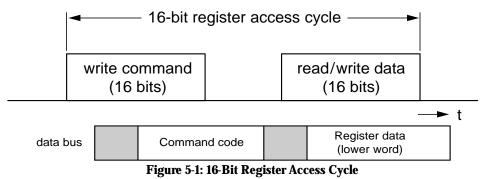

Since the data bus in ISP1161x is 16-bit wide, 32-bit registers are read or written in two data cycles. Figure 5-1 illustrates a 16-bit register access cycle.

In Figure 5-1, a *command code* is the offset index of the register being accessed. Therefore, for example, to write a value into the *HcScratch* register, the HCD will put the offset index of A8H on the data bus followed by a single 16-bit value. To read the *HcScratch* register, the HCD will put the offset index of the register on the data bus and read a single 16-bit data from the data bus.

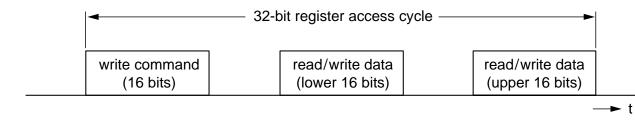

Figure 5-2: 32-Bit Register Access Cycle

To write to a 32-bit register, the HCD will put the offset index of the register on the data bus followed by two consecutive 16-bit data. To read, the HCD will put the offset index of the register on the data bus and read two consecutive 16-bit data from the data bus.

The sample code in Figure 5-3 shows a 32-bit register access with ISP1161x connected to an ISA bus in the x86 platform with two ISA ports assigned to the Host Controller of ISP1161x: the command and data ports.

| #define DATA_PORT                                                  |            | Use the data poi | ,       | ) address | 0x290 | for | the | Host | Controller |

|--------------------------------------------------------------------|------------|------------------|---------|-----------|-------|-----|-----|------|------------|

| #define COMMAND_PORT                                               | 0x292; //  | -                | PC's I/ | ) address | 0x292 | for | the | Host | Controller |

| unsigned long uReg, u                                              | RegData, u | ıData;           |         |           |       |     |     |      |            |

| The <i>HcControl</i> register writes the offset index.             |            |                  |         |           |       |     |     |      |            |

| uReg = 0x81; // HcControl write is 0x81<br>uRegData = 0x00010020;  |            |                  |         |           |       |     |     |      |            |

| Write the offset index to the command port.                        |            |                  |         |           |       |     |     |      |            |

| outw(COMMAND_PORT, uRe                                             | eg);       |                  |         |           |       |     |     |      |            |

| Write data to the data port.<br>Write the lower 16-bit data first. |            |                  |         |           |       |     |     |      |            |

| uData = uRegData & 0x0                                             | 000FFFF;   |                  |         |           |       |     |     |      |            |

outw(DATA\_PORT, uData);

Write the higher 16-bit data. For 16-bit register write, this step is not necessary.

uData = (uRegData & 0xFFFF0000) >> 16; // AND followed by right bit shift of 16 bits outw(DATA\_PORT, uData);

Figure 5-3: Code Example for 32-Bit Register Write

In the preceding example, the command and data ports are 16-bit wide. The *outw()* function is an x86 assembly routine that writes a 16-bit data to the specified port.

The following example code reads data from a 32-bit register.

unsigned long uRegData;

The *HcControl* register writes the offset index.

uHcControlReg = 0x01; // HcControl register read is 0x01

Write the offset index to the command port.

outw(COMMAND\_PORT, uHcControlReg);

Read the lower 16-bit data from the data port.

uData = inw(DATA\_PORT);

Save the lower 16-bit data.

uRegData = uData & 0x0000FFFF;

Read the higher 16-bit data and concatenate the lower and higher 16-bit data. For 16-bit read, this step is not required.

uData = inw(DATA\_PORT); uRegData |= (uData & 0x0000FFFF) << 16;

#### Figure 5-4: Code Example for 32-Bit Register Read

The function in *w()* is an x86 assembly routine that reads a 16-bit data from the specified port.

The code example in Figure 5-5 reads a 16-bit value from a 16-bit register.

unsigned long uRegData;

The *HcScratch* register reads the offset index.

uHcScratchReg = 0x28;

Write the offset index to the command port.

outw(COMMAND\_PORT, uHcScratchReg);

Read the 16-bit register value from the data port.

uData = inw(DATA\_PORT);

Figure 5-5: Code Example for 16-Bit Register Read

The code example in Figure 5-6 writes a 16-bit value to a 16-bit register.

unsigned long uData;

The *HcScratch* register writes the offset index.

uScratchReg = 0xA8; uData = 0xAA55;

Write the offset index to the command port.

outw(COMMAND\_PORT, uScatchReg);

Write the 16-bit data to the data port.

outw(DATA\_PORT, uData);

#### Figure 5-6: Code Example for 16-Bit Register Write

Throughout this document, pseudo function calls—WRITE\_32BIT\_REG(), READ\_32BIT\_REG(), WRITE\_16BIT\_REG() and READ\_16BIT\_REG()—will be used in code examples to depict read/write access to ISP1161x internal registers.

### 5.3. Writing and Reading of the ATL and ITL Buffers

The ATL and ITL buffers are physically located in the FIFO buffer RAM inside ISP1161x. Each buffer contains a list of PTDs that the Host Controller hardware uses to send or receive USB packets to or from USB slave devices. As part of scheduling USB transfers, the HCD constructs PTDs in the system memory and then moves the constructed PTDs to the ATL or ITL buffer. The Host Controller hardware allows software to access each buffer as if they are separate hardware buffers. The HCD accesses the ATL buffer by using the hardware registers—*HcTransferCounter* (22H/A2H) and *HcATLBufferPort* (41H/C1H)—and the ITL buffer by using *HcTransferCounter* and *HcITLBufferPort* (40H/C0H).

The example code in Figure 5-7 shows how to write and read to and from the ATL buffer in the PIO mode.

void fnv1161AtlWrite(char \* pbyChar, unsigned long uTotalByte)

| unsigned | long | uTotalDoubleWord; |

|----------|------|-------------------|

| unsigned | long | * puLong;         |

| unsigned | long | uIndex;           |

| unsigned | long | uData1;           |

| unsigned | long | uData2;           |

Program the 16-bit transfer counter register: *HcTransferCounter*. Make sure that bit 7 of the register offset index is 1.

outw(COMMAND\_PORT, HcTransferCounter | 0x80); outw(DATA\_PORT, uTotalByte);

Express the total number of bytes to be transferred in terms of double word. Typecast the byte aligned data buffer to double word aligned buffer.

uTotalDoubleWord = uTotalByte >> 2; puLong = (unsigned long \*) pbyChar;

Write the *HcATLBufferPort* register offset index to the command port. Make sure that bit 7 of the register offset index is 1.

outw(COMMAND\_PORT ,HcATLBufferPort | 0x80));

Wait a while before writing data bytes. Each *iodelay()* causes 1 system tick delay. There must be a minimum of 300 ns delay between the command and data phases.

iodelay(); iodelay(); iodelay();

Disable all hardware interrupts during the data write.

cli();

Write data to the ATL buffer by writing to the data port 16 bits at a time.

```

for (uIndex = 0; uIndex < uTotalDoubleWord; uIndex ++)

{

uData1 = puLong[uIndex] & 0x0000FFFF;

uData2 = (puLong[uIndex] & 0xFFFF0000) >> 16;

outw(DATA_PORT,uData1); // Write lower 16-bit first

outw(DATA_PORT,uData2); // Write higher 16-bit

```

| Rev.                                      | 1 | 1 | n  |

|-------------------------------------------|---|---|----|

| $\mathbf{N} \mathbf{\nabla} \mathbf{V}$ . |   |   | ., |

}

# ISP1161x Embedded Programming Guide

// There must be a minimum of a 112 ns delay between data phases.

iodelay();

}

Enable all hardware interrupts when the write is done.

sti();

# Figure 5-7: Code Example for Writing to the ATL Buffer

### 5.4. Typical Hardware Initialization Sequence

When the ISP1161x hardware is powered on, the Host Controller Driver (HCD) must go through the following hardware initialization steps to set the Host Controller into the operational state.

**Note**: In addition to the hardware initialization steps described later, the HCD must also initialize necessary data structures in between the hardware initialization steps. The requirements for the initialization of data structures differ depending on the underlying operating system and description of data structures is outside the scope of this document.

- 1. Detecting the Host Controller

- 2. Software resetting the Host Controller

- a. Setting the Host Controller to the RESET state

- 3. Configuring the *HcHardwareConfiguration* register

- a. Setting the interrupt output polarity

- b. Setting the interrupt trigger mode between level triggered and edge triggered

- c. Enabling the global interrupt INT1

- d. Setting DMA related modes, if DMA is used

- i. DACK input polarity

- ii. DREQ output polarity

- 4. Configuring interrupts

- a. USB specific interrupts

- i. Master interrupt enable

- ii. Root hub status change interrupt

- iii. Frame number overflow interrupt

- iv. Unrecoverable error interrupt

- v. Resume detect interrupt

- vi. Start-of-Frame (SOF) interrupt

- vii. Scheduling overrun interrupt

- b. Host Controller related interrupts

- i. Clock ready interrupt

- ii. Host Controller suspend interrupt

- iii. OPR register interrupt

- iv. All EOT interrupt

- v. ATL done interrupt

- vi. SOF ITL done interrupt

- 5. Configuring the *HcControl* register

- a. Setting remote wake-up enable

- b. Setting remote wake-up connected

- 6. Configuring the *HcFmInterval* register

- 7. Configuring the root hub registers

- a. HcRhDescriptorA register

- b. HcRhDescriptorB register

- c. HcRhStatus register

- 8. Setting the ITL and ATL buffer lengths

- 9. Installing the INT1 interrupt service routine

- 10. Setting the Host Controller to the operational state.

### 5.4.1. Detecting the Host Controller

The detection of the Host Controller is done by the HCD by writing a value to the *HcScratch* register (see Table 5-2), reading from the *HcScratch* register and comparing the expected and actual values of the register. If the two values match, the HCD concludes that the Host Controller is present. The correct *HcChipID* read can also be used as an extra condition for detection of the Host Controller.

#### Table 5-2: HcScratch Register: Bit Allocation

| I ubic 0 # | . Hestiden  | The store of the s | mocution |    |    |    |   |   |  |

|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----|----|----|---|---|--|

| READ INL   | DEX—28H; WK | RITE INDEX-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -A8H     |    |    |    |   |   |  |

| Bit        | 15          | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13       | 12 | 11 | 10 | 9 | 8 |  |

| Symbol     |             | Scratch[15:8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |    |    |    |   |   |  |

| Reset      | 0           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0        | 0  | 0  | 0  | 0 | 0 |  |

| Access     |             | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |    |    |    |   |   |  |

| Bit        | 7           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5        | 4  | 3  | 2  | 1 | 0 |  |

| Symbol     |             | Scratch[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |    |    |    |   |   |  |

| Reset      | 0           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0        | 0  | 0  | 0  | 0 | 0 |  |

| Access     |             | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |    |    |    |   |   |  |

The pseudocode for detecting an ISP1161x Host Controller is given in Figure 5-8.

#### Figure 5-8: Code Example for Detecting the Host Controller

### 5.4.2. Software Resetting the Host Controller

The software reset of the Host Controller involves two steps:

1. Resetting the Host Controller

2. Setting the Host Controller to the RESET state.

The HCD resets the Host Controller by setting the HCR bit in the *HcCommandStatus* register (see Table 5-3). Since it takes a while (about 10  $\mu$ s) to reset the Host Controller, the HCD must wait for at least 10  $\mu$ s before it proceeds. A pseudocode for resetting the Host Controller is given in Figure 5-9.

```

// Read the contents of the HcCommandStatus register.

uValue = READ_32BIT_REG(HcCommandStatus);

// Set the HCR bit

uValue |= 0x00000001;

WRITE_32BIT_REG(hcCommandStatus, uValue);

// Wait until reset is done. When reset is done, the HCR bit is set to logic 0.

While (READ_32BIT_REG(HcCommandStatus & 0x0000001));

```

#### Table 5-3: HcCommandStatus Register: Bit Allocation

| READ IND | EX—02H; WR | ITE INDEX—        | - <i>82H</i> |          |      |    |    |     |  |  |  |

|----------|------------|-------------------|--------------|----------|------|----|----|-----|--|--|--|

| Bit      | 31         | 30                | 29           | 28       | 27   | 26 | 25 | 24  |  |  |  |

| Symbol   |            |                   |              | rese     | rved |    |    |     |  |  |  |

| Reset    |            |                   |              | 00       | )H   |    |    |     |  |  |  |

| Access   |            |                   |              | í        | ۲    |    |    |     |  |  |  |

| Bit      | 23         | 22                | 21           | 20       | 19   | 18 | 17 | 16  |  |  |  |

| Symbol   |            | reserved SOC[1:0] |              |          |      |    |    |     |  |  |  |

| Reset    | 0          | 0                 | 0            | 0        | 0    | 0  | 0  | 0   |  |  |  |

| Access   |            |                   | F            | ۲        |      |    | F  | R   |  |  |  |

| Bit      | 15         | 14                | 13           | 12       | 11   | 10 | 9  | 8   |  |  |  |

| Symbol   |            |                   |              | rese     | rved |    |    |     |  |  |  |

| Reset    |            |                   |              | 00       | )H   |    |    |     |  |  |  |

| Access   |            |                   |              | R        | W    |    |    |     |  |  |  |

| Bit      | 7          | 6                 | 5            | 4        | 3    | 2  | 1  | 0   |  |  |  |

| Symbol   |            |                   |              | reserved |      |    |    | HCR |  |  |  |

| Reset    | 0          | 0                 | 0            | 0        | 0    | 0  | 0  | 0   |  |  |  |

| Access   |            |                   |              | R        | w    |    |    |     |  |  |  |

Once the Host Controller is reset, the HCD must set the Host Controller to the RESET state by writing 00B to the HCFS field in the *HcControl* register (see Table 5-4). This step completes resetting of the Host Controller.

uValue = READ\_32BIT\_REG(HcControl);

```

// When writing a new value to the HcControl register, the state of other bits in the register

// must be preserved by writing 1 to the bits already set to 1 in the register.

uValue &= ~0x000000000;

// 00B in bit[7:6] => RESET state

uValue |= 0x00000000

```

WRITE\_32BIT\_REG (HcControl, uValue);

```

Figure 5-10: Code Example for Setting the Host Controller to the RESET State

```

Table 5-4: HcControl Register: Bit Allocation

READ INDEX-01H; WRITE INDEX-81H

| Bit    | 31   | 30     | 29       | 28   | 27   | 26   | 25  | 24       |

|--------|------|--------|----------|------|------|------|-----|----------|

| Symbol |      |        |          | rese | rved |      |     |          |

| Reset  |      |        |          | 00   | ЭH   |      |     |          |

| Access | R/W  | R/W    | R/W      | R/W  | R/W  | R/W  | R/W | R/W      |

| Bit    | 23   | 22     | 21       | 20   | 19   | 18   | 17  | 16       |

| Symbol |      |        |          | rese | rved |      |     |          |

| Reset  |      |        |          | 00   | )H   |      |     |          |

| Access | R/W  | R/W    | R/W      | R/W  | R/W  | R/W  | R/W | R/W      |

| Bit    | 15   | 14     | 13       | 12   | 11   | 10   | 9   | 8        |

| Symbol |      |        | reserved |      |      | RWE  | RWC | reserved |

| Reset  | 0    | 0      | 0        | 0    | 0    | 0    | 0   | 0        |

| Access | R/W  | R/W    | R/W      | R/W  | R/W  | R/W  | R/W | R/W      |

| Bit    | 7    | 6      | 5        | 4    | 3    | 2    | 1   | 0        |

| Symbol | HCFS | S[1:0] |          |      | rese | rved |     |          |

| Reset  | 0    | 0      | 0        | 0    | 0    | 0    | 0   | 0        |

| Access | R/W  | R/W    | R/W      | R/W  | R/W  | R/W  | R/W | R/W      |

### HCFS (Host Controller Functional State)—Bits[7 to 6]

- 00B—RESET

- 01B—RESUME